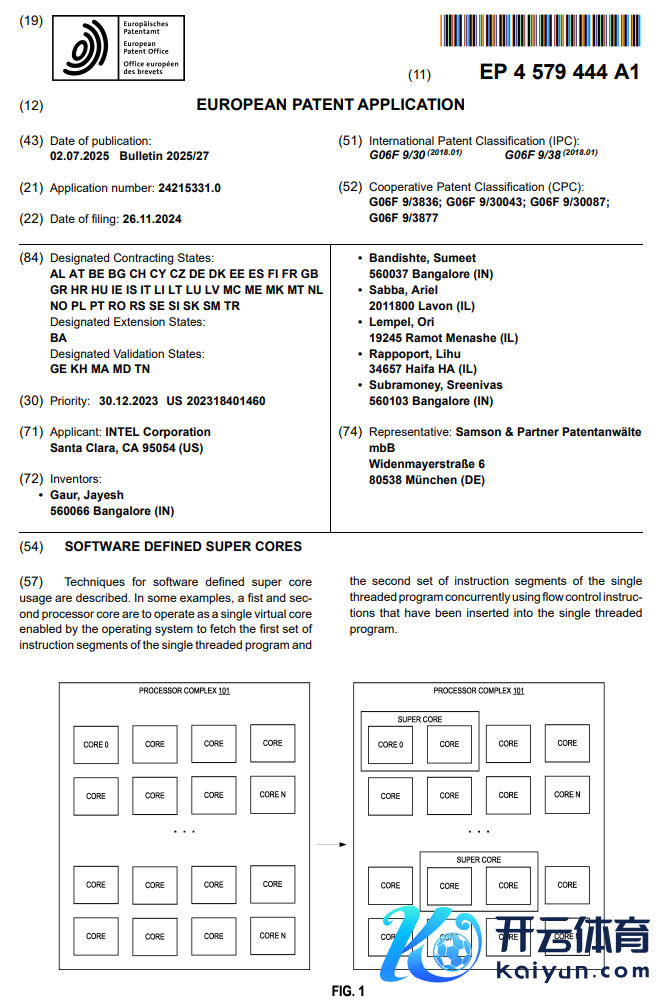

IT之家 8 月 31 日音书,Reddit 网友昨天挖出了一项名为“软件界说超等中枢”(Software Defined Super Cores, SDC)的专利开云体育,编号为 EP4579444A1。

该手艺旨在不依赖硬件界限彭胀或制程工艺升级的情况下,通过软件协调多中枢协同职责,权贵增强单线程处置技艺。

从字面预想上来看,该手艺旨在让两个或多个 CPU 中枢协同职责,就像一个超大中枢雷同,听起来很像奔腾 4 期间流传的“逆超线程”传奇。还有东说念主研究,这与英特尔取消的“皇家中枢”(Royal Core)口头存在某种相关。

关于各人熟识的传统 CPU 来说,单个物理中枢的性能擢升存在边缘效益递减问题,是以业界更多依赖于制程与频率的擢升来提高单核性能。

灵验户以为,英特尔比年来力推 P+E 核的混杂架构实属无奈之举,其中的 E 核实质上手艺比 P 核更先进,但若何 E 核无法独自扛起大旗。

好多用户但愿英特尔能推出一款全 P 核的处置器(Bartlett Lake 仅面向镶嵌式平台),但短期内惟恐很难,以致道路图露出 2028 年的 Titan Lake 将全都毁掉 P 核(提供最高 100 个 E 核)。

英特尔本次公布的专利露出,英特尔但愿其 CPU 或者将行为拆分红多个代码块,从而将总共任务分布到多个并行的小核上协调加快完成,而不是猝然元气心灵去构建费电的大核。

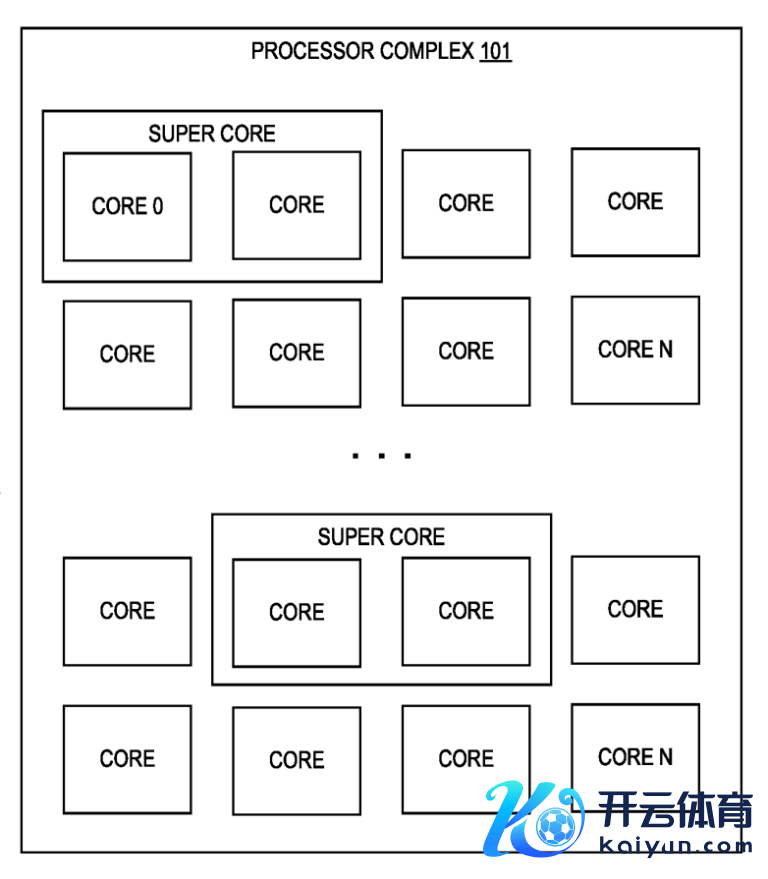

从操作系统视角来看,这些协同职责的中枢组仍被视为和洽的逻辑中枢(无需软件层适配),但施行上是多个中枢在协同职责。

从用户角度来看,这一手艺似乎或者将两个或多个较小的中枢动态团聚为一个更大的“超等中枢”,完毕对单线程任务的高效处置。

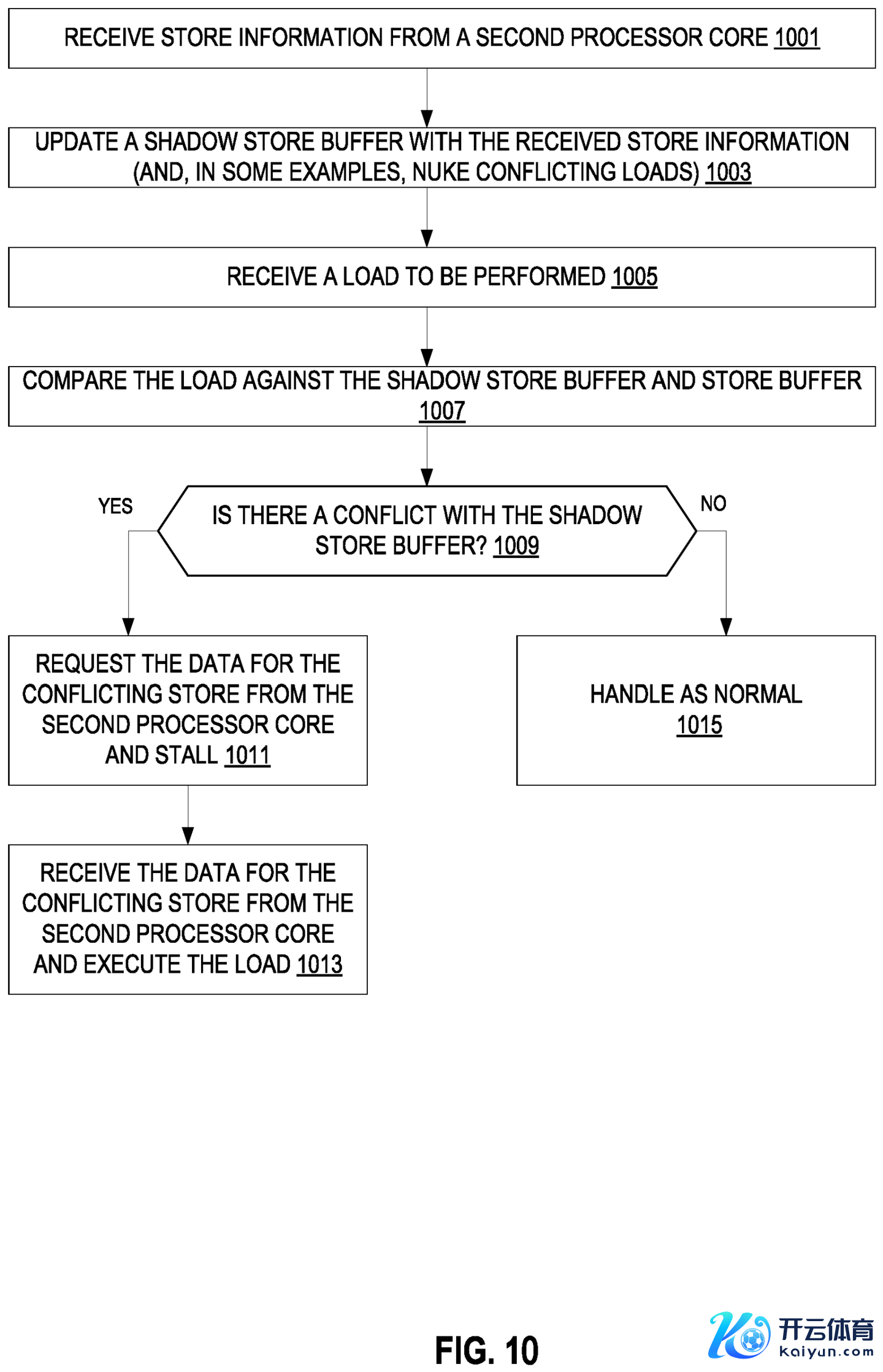

尽管多中枢协同职责濒临辅导限定珍惜与数据同步等手艺挑战,但英特尔在专利中宣称,SDC 手艺可通过稀奇辅导及“影子存储缓冲区”(Shadow Store Buffer)等机制保险中枢间数据传递的准确性。

值得扎眼的是,该手艺并非多线程并行处置,而是针对单线程操作的专项优化。其上风在于无需提高电压或频率即可擢升 IPC,尤其适用于突发性高负载单线程任务。证明专利形色,CPU 可证明负载需求动态在“老例中枢”与“超等中枢”之间来去切换。

现在该手艺仍处于专利阶段,施行欺诈需克服中枢间低蔓延通讯、操作系统改换适配等工程化辛勤。业界关爱该手艺能否欺诈于英特尔将来处置器架构中,IT之家后续也将保捏关爱,敬请期待。